AMD’s new Ryzen 7000 desktop CPUs, based on the Zen4 micro-architecture, still use the same chiplet design as their predecessors, with some minor but not minor changes. Igor gave information about this in a big review yesterday. Today we want to tackle how to configure the new CPU as best as possible and for that we test no less than 10 different configurations of memory ICs, rank, clock rate, timing and of course Infinity Fabric speed. are. Many thanks to ASRock, AMD, for whose support we were able to prepare this guide in time for launch.

What’s new in Zen 4, AM5 and Ryzen 7000?

But what’s really new in the Zen 4 Raphael compared to the Zen 3 Vermeer and how does that affect the adjustment screws left to each user? Since the design with 1-2 compute cluster dies (CCD) and one IO die, the infinite fabric connecting with its clock rate (FCLK) is still of high importance. The IO die then communicates with the rest of the system as usual via interfaces such as PCIe 5.0 and DDR5. The number of RAM channels also remains the same, effectively 2x with 64bit.

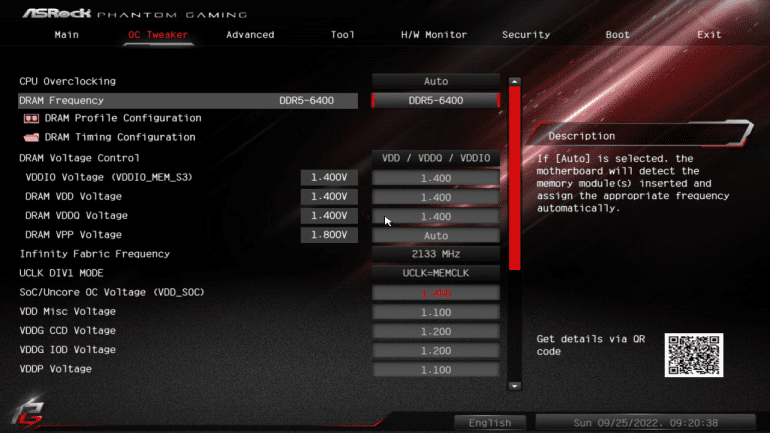

The RAM “sweet spot” has changed from DDR4-3600 on the Zen 3 to DDR5-6000 on the Zen 4, and it’s really there. No, AMD, don’t forget the originally advertised 2000MHz FCLK with DDR4-4000 on the Zen 3, which never really worked, but luckily it’s different this time. Infinity Fabric or FCLK also runs slightly faster than the Zen 3, but by no means at 3000MHz. As a result, there may no longer be a 1:1:1 configuration with the DDR5-6000, as with the Zen 3.

At RAM clock rates greater than 6000 Mbps, UCLK automatically switches to 1/2:1 mode, known as 1:2. For example, if you activate an EXPO profile with DDR4-6400, the corresponding values are 3200 MHz for MCLK and 1600 MHz for UCLK. FCLK remains capped at 2000 MHz, at least until you change it manually. With a RAM clock rate below DDR5-6000, an average value between a base clock of 1800 MHz and a maximum of 2000 MHz is automatically set for FLCK, for example 1900 MHz with DDR5-5600.

The already mentioned expo profile is technically nothing more than an XMP profile with a different memory address, really. The stored time and voltage are the same, only that they have a different sticker and further back to the SPD. As a result, it is also possible for RAM Kits to put together XMP and Expo profiles with the appropriate customization for each platform.

Well-known RAM manufacturers are already working on kits with both standards, and those who don’t want to wait can flash an Expo profile onto their XMP kit and vice versa. Not that this would be necessary, because at least on a Zen 4 mainboard, an XMP profile can be loaded directly into the BIOS without any further ado. Reminds me of the G-Sync vs Adaptive Sync saga, although AMD followed with the open standard and slowly but surely phased out the proprietary certification policy, but I hold back again.

Internet fan. Alcohol expert. Beer ninja. Organizer. Certified tv specialist. Explorer. Social media nerd.